## Safe Automotive soFtware architEcture (SAFE)

Contract number: ITEA2 – 10039

ITEA Roadmap application domains:

Major: Services, Systems & Software Creation

Minor: Society

ITEA Roadmap technology categories:

Major: Systems Engineering & Software Engineering

Minor 1: Engineering Process Support

## WP3 - Deliverable D3.2.2

# Proposal for extension of Meta model for hardware modeling

Due date of deliverable: 28/02/2013 Actual submission date: 28/02/2013

Start date of the task: 13/12/2011

Duration: 15 months

Task coordinator name: Philippe Cuenot Organization name of lead contractor for this deliverable: Continental France

Editor: Philippe Cuenot Contributors: Philippe Cuenot, Nico Adler, Stefan Otten Reviewers: Florent Meurville, Martin Hillenbrand

#### Revision chart and history log

| Version | Date       | Reason                                                                                                  |

|---------|------------|---------------------------------------------------------------------------------------------------------|

| 0.1     | 2012-07-17 | Initialization of document                                                                              |

| 0.2     | 2012-12-14 | Revision of template and allocation                                                                     |

| 0.3     | 2013-01-23 | Initial documentation of contribution to SAFE meta model and inter-<br>dependencies to other work tasks |

| 0.4     | 2013-02-05 | Conti-F contributions chap 4 to 6.                                                                      |

| 0.5     | 2013-02-06 | Meta model documentation, Hardware modeling scoping, Performing<br>Hardware Modeling based on EAST-ADL  |

| 0.6     | 2013-02-08 | Review of Chapter 6 by Florent for WT331 interface                                                      |

| 0.7     | 2013-02-19 | Current status EAST-ADL + chap. 7 and 9                                                                 |

| 0.8     | 2013-02-21 | Update MM description                                                                                   |

| 0.9     | 2013-02-22 | New chapter 8.3, 8.4, 9.2 and completion of chap 10 and 11                                              |

| 1.0     | 2013-02-28 | Final version 1.0 with proof reading                                                                    |

1

#### Table of contents

| 1  | Tab   | le of contents                                                          | 3  |

|----|-------|-------------------------------------------------------------------------|----|

| 2  | List  | of figures                                                              | 5  |

| 3  | Exe   | cutive Summary                                                          | 6  |

| 4  | Intro | oduction and overview of document                                       | 7  |

| 4  | 4.1   | Scope of WT 3.2.2                                                       |    |

|    | 4.2   | Structure of document                                                   |    |

| 5  |       | rview on ISO 26262                                                      |    |

| 6  | Safe  | ety Analysis Methods Interface                                          | 14 |

| (  | 6.1   | Interface Methodology for Safety Analysis                               | 14 |

| (  | 6.2   | Interface Element                                                       | 17 |

| 7  | Har   | dware modeling scoping                                                  | 19 |

| -  | 7.1   | Requirements Package: Hardware Components                               | 19 |

| -  | 7.2   | Requirements Package: Hardware Failure                                  | 19 |

| -  | 7.3   | Requirements Package: Hardware Architectural Metrics                    | 20 |

| -  | 7.4   | Requirements Package: Safety Goal Violation                             | 20 |

| -  | 7.5   | Requirements Package: Traceability                                      | 20 |

| -  | 7.6   | Allocation of the requirements packages to derived meta model structure | 20 |

| 8  | Per   | orming Hardware Modeling based on EAST-ADL                              | 22 |

| 8  | 8.1   | Current status of EAST-ADL                                              | 22 |

| 8  | 8.2   | Proposed extensions to EAST-ADL                                         | 26 |

| 8  | 8.3   | Current status of AUTOSAR                                               | 27 |

| 8  | 8.4   | Proposed extensions to AUTOSAR                                          | 28 |

| 9  | WT    | 3.2.2 Contribution to SAFE Meta-Model                                   | 29 |

| ę  | 9.1   | Overview                                                                | 29 |

| ę  | 9.2   | Proposal for change request on EAST-ADL                                 | 31 |

|    | 9.2.  | 1 Package Hardware Structure                                            |    |

| ę  | 9.3   | Detailed Description of Classes and Links of Package Hardware           | 57 |

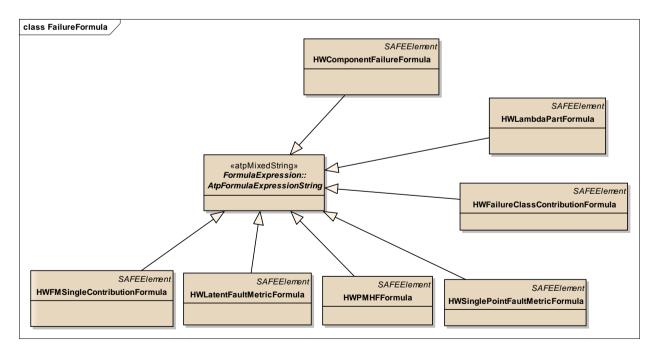

|    | 9.3.  | 1 Package FailureFormula                                                | 57 |

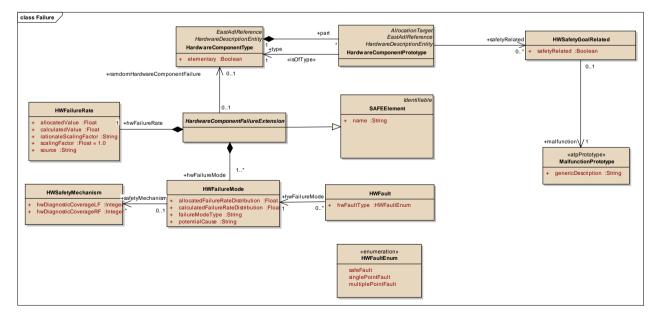

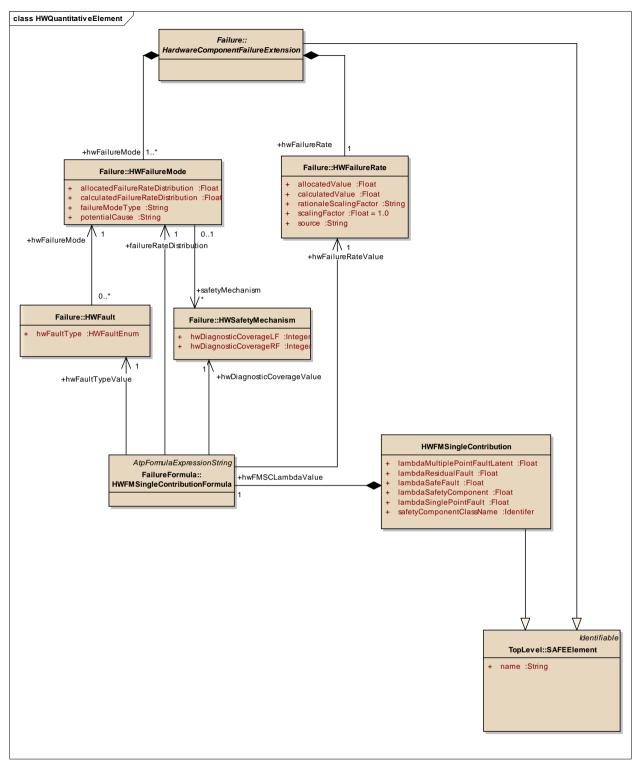

|    | 9.3.  | 2 Package Failure                                                       | 64 |

|    | 9.3.  | 3 Package HWQuantitativeMeasure                                         | 79 |

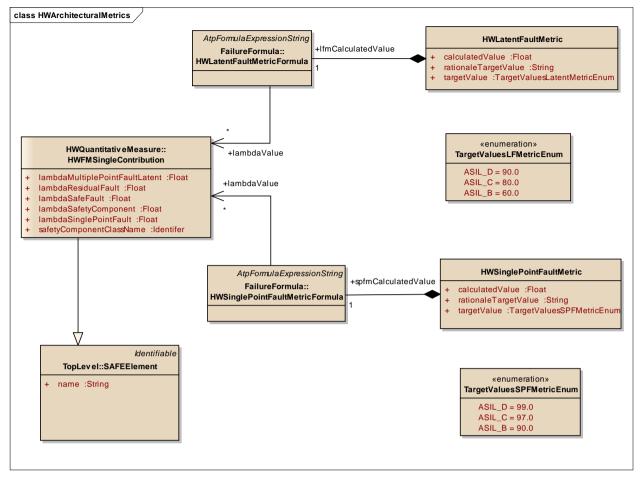

|    | 9.3.  | 4 Package HWArchitecturalMetrics                                        | 83 |

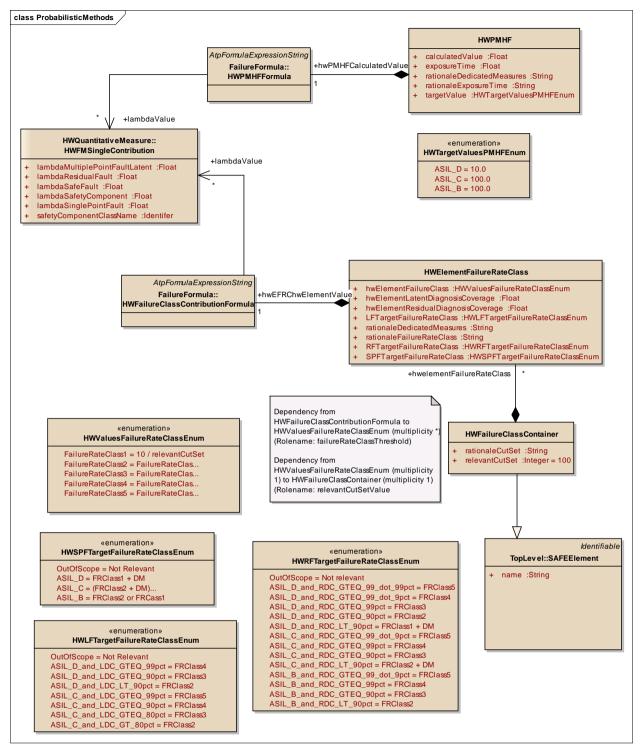

|    | 9.3.  | 5 Package ProbabilisticMethods                                          | 87 |

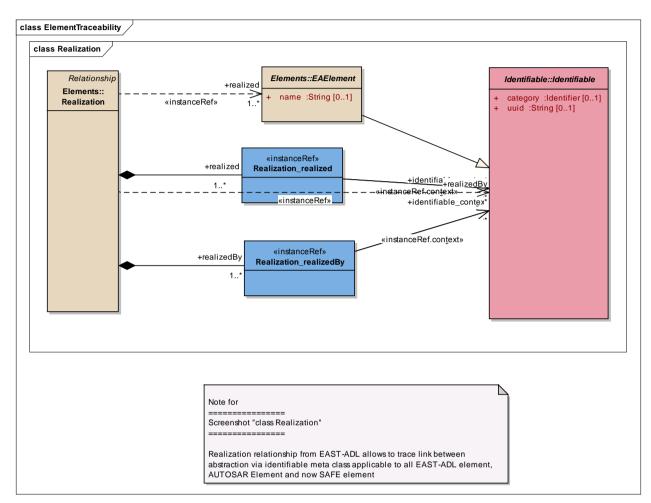

|    | 9.3.  | 6 Package Traceability                                                  | 97 |

| 10 | D     | escription Based on an Example                                          | 99 |

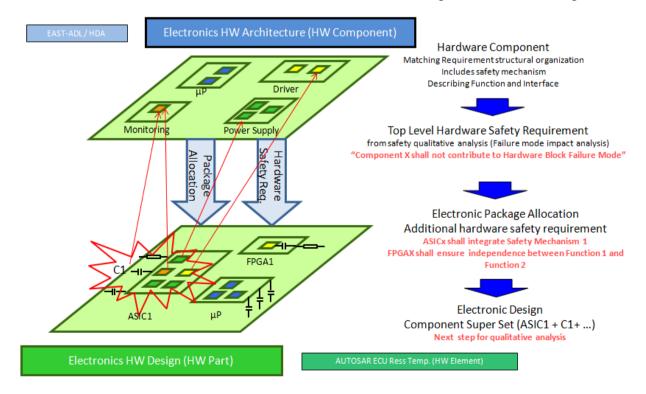

| 1    | 0.1.1  | Step 1: Capture Hardware Technical Safety Concept                            | 100 |

|------|--------|------------------------------------------------------------------------------|-----|

| 1    | 0.1.2  | Step 2: Complete HW Component Failure Propagation on Hardware Architecture   | 100 |

| 1    | 0.1.3  | Step 3: Define target values for HW Components and calculates metrics        | 101 |

| 1    | 0.1.4  | Step 4: Define Hardware Part Allocation and Malfunction                      | 101 |

| 1    | 0.1.5  | Step 5: Develop Electronics Schematic                                        | 101 |

| 1    | 0.1.6  | Step 6: Perform Electronic FMEA and contribution to HW Component malfunction | 101 |

| 1    | 0.1.7  | Step 7: Verify Component Metrics and Probabilistic value                     | 101 |

| 11   | IP-XAC | T interchange                                                                | 102 |

| 11.1 | Мар    | bing rules                                                                   | 104 |

| 11.2 | 2 Exte | nsion for failure information                                                | 106 |

| 12   | Conclu | sions and Discussion                                                         | 107 |

| 13   | Refere | nces                                                                         | 108 |

| 14   | Acknov | vledgments                                                                   | 109 |

# 2 List of figures

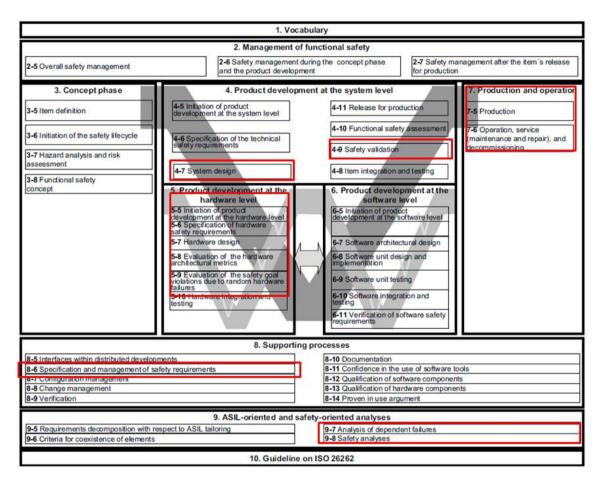

| Figure 1: Overview on ISO 26262 (Relevant parts highlighted)                 | 10  |

|------------------------------------------------------------------------------|-----|

| Figure 2: Overview on structure of architecture (Relevant parts highlighted) | 15  |

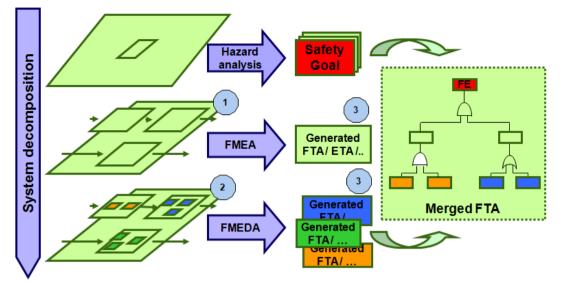

| Figure 3: Overview on iterative safety analysis methods                      | 16  |

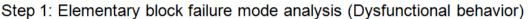

| Figure 4: Hardware allocation and quantitative analysis                      | 16  |

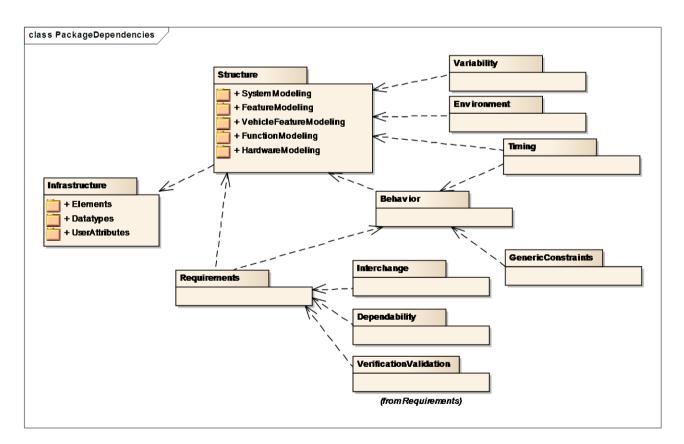

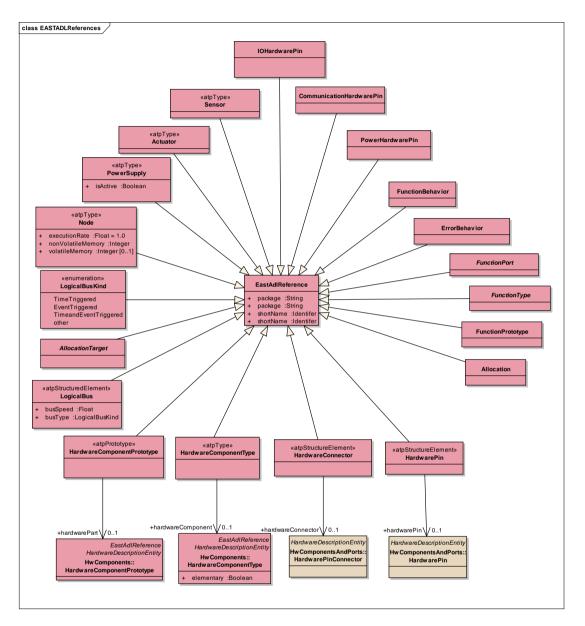

| Figure 5: Class diagram for Package Dependencies                             | 22  |

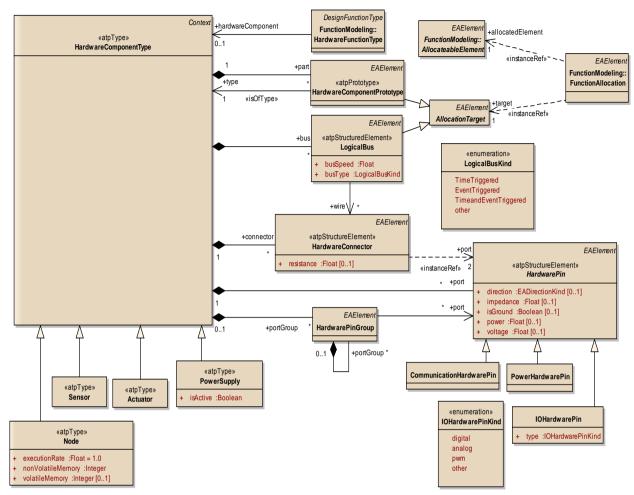

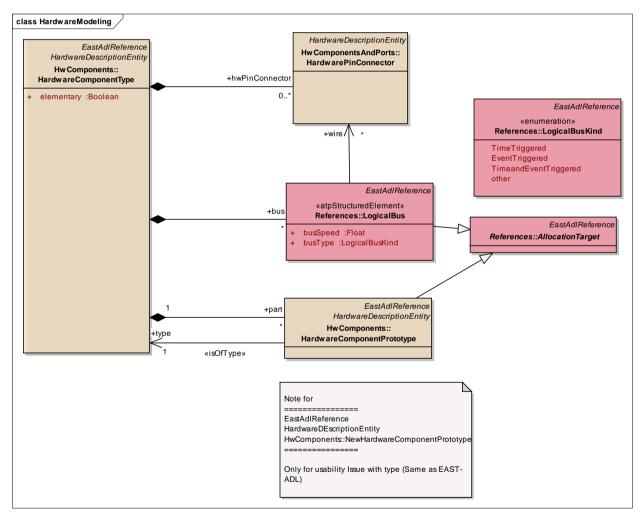

| Figure 6: Class diagram for Hardware Modeling in the EAST-ADL2               | 23  |

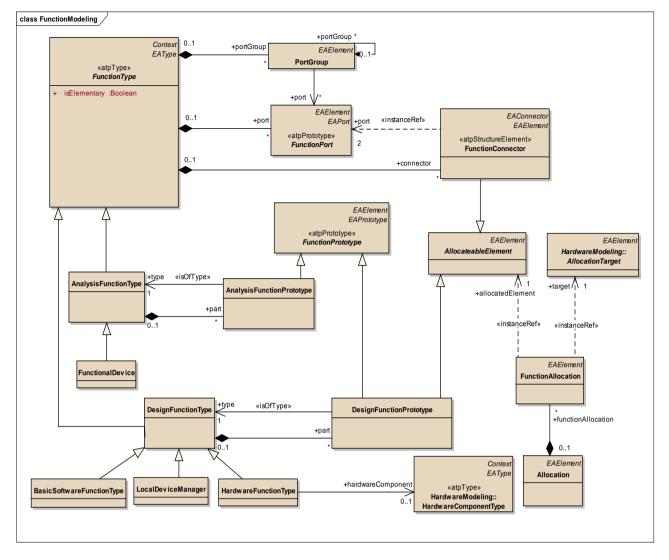

| Figure 7: Class diagram for Function Modeling in the EAST-ADL2               | 24  |

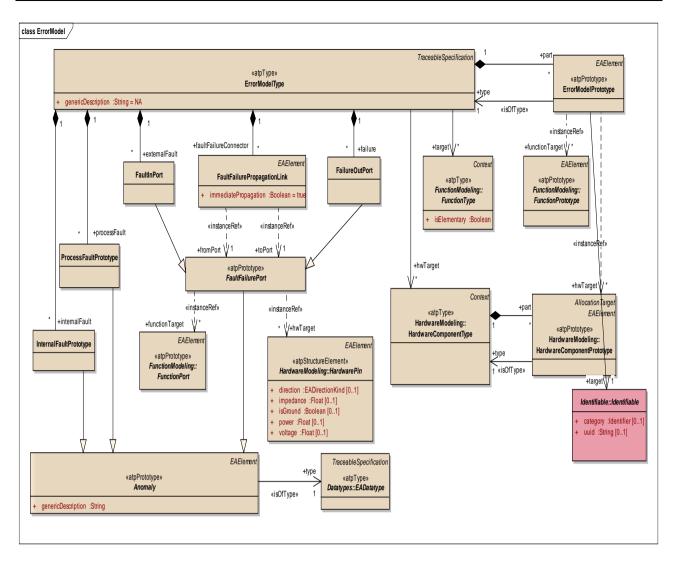

| Figure 8: Class diagram for Error Modeling in the EAST-ADL2 Dependability    | 25  |

| Figure 9: Class diagram for Error Behavior in the EAST-ADL2 Dependability    | 26  |

| Figure 10: AUTOSAR ECU Resource overview                                     | 27  |

| Figure 11: Overview on WT 3.2.2-contribution to SAFE meta-model              | 29  |

| Figure 12: References of package Hardware to EAST-ADL                        | 30  |

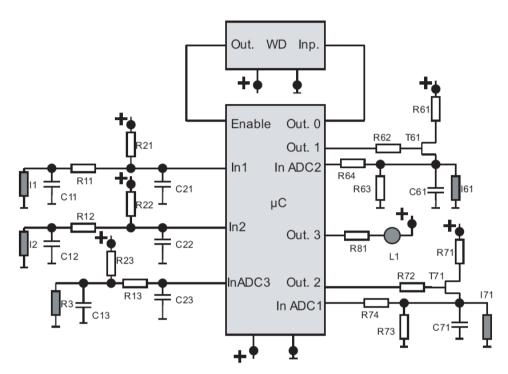

| Figure 13: Electronic Schematic diagram ISO26262-Part5 Figure E.1            | 99  |

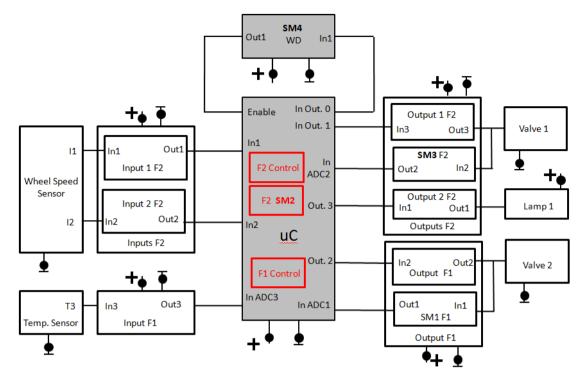

| Figure 14: Technical Safety Concept for ISO26262-Part5 Figure E.1            | 100 |

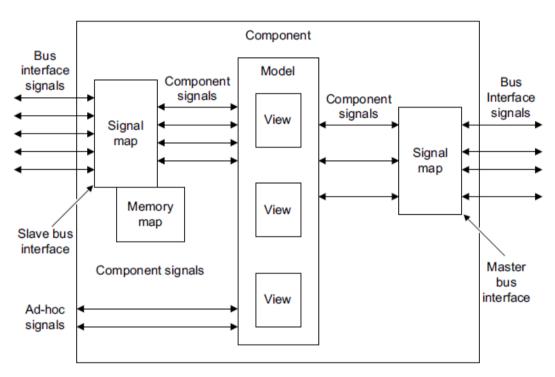

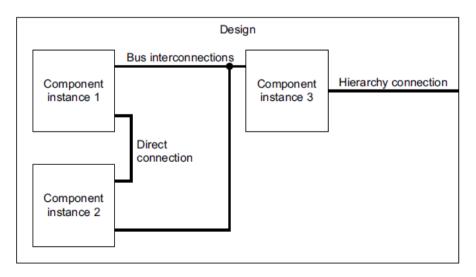

| Figure 15: Structure of a component IP-XACT                                  | 102 |

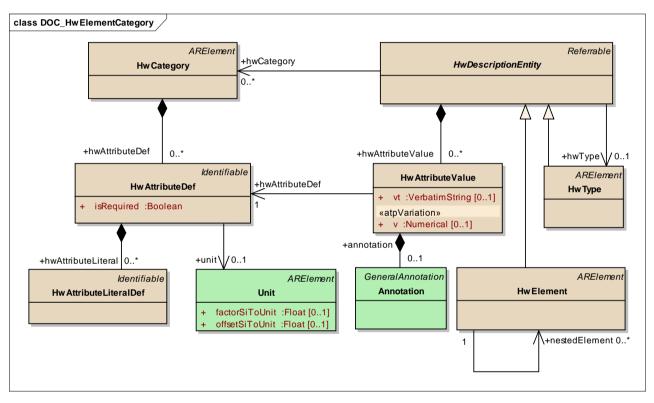

| Figure 16: Design representation in IP-XACT                                  | 102 |

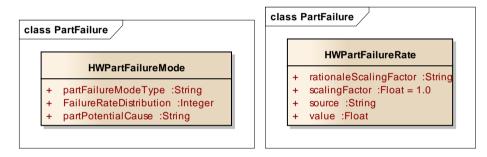

| Figure 17: AUTOSAR HWcomponent and HWCategory                                | 103 |

| Figure 18: Class mapping between AUTOSAR and IP-XACT                         | 105 |

| Figure 19: Hardware Part Failure information for IP-XACT                     | 106 |

#### 3 Executive Summary

The work task WT3.2.2 targets the topics of definition of hardware modeling. This activity includes the definition of the necessary elements to represent the hardware architecture of the technical safety concept and the hardware parts of electronic schematics. It also comprises the modeling constructs enabling the calculation of hardware quantitative measures required by the ISO 26262 [1] for hardware architectural metrics and the safety goal evaluation due to random hardware failures.

Besides giving an overview of relevant sections in ISO 26262 the allocated requirements to WT3.2.2 resulting from an ISO 26262 analysis of WT 2.1 and the needs from use case descriptions in WT2.3 are presented.

In addition to the previous mentioned overview the initial methodology for hardware technical safety concept representation, for hardware component failure mode and rating definition in accordance with the needs of ISO 26262 is presented. As it is objective to develop a meta-model for hardware modeling the current version of EAST-ADL[3] and AUTOSAR[2] is analyzed. Moreover, the contribution of WT3.2.2 to the SAFE meta-model, which is based on EAST-ADL is presented.

The relation of selected hardware meta model constructs with consumer electronic interchange format IP-XACT [4] from Accelera Organization is discussed. A first overview of proposed links is given.

#### 4 Introduction and overview of document

This document at hand provides information about a methodology for hardware modeling to facilitate the representation and to perform the safety evaluation of the technical safety concept related to hardware equipment and electronics components. The proposed method will rely on existing automotive standards AUTOSAR and EAST-ADL, and will forecast to elaborate of first approach to connect it to consumer electronics standard IP-XCAT.

#### 4.1 Scope of WT 3.2.2

Work task WT3.2.2 deals with hardware description.

Basis is the hardware design architecture of EAST-ADL [3] and the ECU resource template from AUTOSAR[2] in the hardware element description, both being presented in chapter 8. WT3.2.2 intends to provide a methodology for the hardware architecture representation and decomposition into component part description, with respect to safety evaluation and quantitative measurement related to random hardware failure. The existing current meta-model of EAST-ADL and AUTOSAR will be analyzed to provide proposals for improvement to basic standards via change request and to define appropriate safety-related extensions in terms of the described topics of WT3.5

Additionally, the IP-XACT [4] interchange format will be mapped to AUTOSAR hardware elements, as component part description, in order to initiate requirements for a possible automatic transformation to favor hardware model exchange with silicon suppliers.

In order to be able to do so, the following artifacts and their interrelations shall be considered:

#### Hardware Component

The applicable concept of EAST-ADL2.1 for hardware components (type and prototype) allows representing a logical or technical hardware element. This actual construct allows compositional organization of hardware elements, either used to represent logical element or directly as a physical electronic component. The use of logical elements allows a functional abstraction of electronic component, then allocated into one (or several) physical electronic complex component (e.g. FPGA, ASIC) or decomposed into a set of physical electronic component (resistors, capacitors, etc...). The hardware component concept shall enable a direct relation to behavioral representation for functional or dysfunctional modeling and possible simulation. Furthermore, the interconnection of component concept for whatever bus interconnection is capable for on low level electronic abstraction features (e.g. SPI, AMBA bus...). The use of hardware components and their interconnections shall also permit flexible and reusable description of hardware characteristics in particular for the ports. This would facilitate the allocation of a hardware component to physical elements based on predefine semi- formal semantic.

#### Hardware Part

The concept for hardware part shall allow depicting the physical implementation of a hardware component, decomposed by multiple electronic parts, to be able to support the description of an electronic design schematic using concrete electronic components (exemplarily resistors, capacitors and complex components). AUTOSAR R4.0 includes hardware element constructs required for software configuration in AUTOSAR ECU Resource Template. The proposed use of hardware part shall enable the use of AUTOSAR hardware elements and define a clear interrelation with hardware component.

#### Hardware Architecture

The concept for Hardware Architecture has to comply with the needs of the Technical Safety Concept description of hardware elements with regards to software elements for the software architecture. The hardware architecture level represents the set of hardware components for the intended features of the system and additionally has to support the introduction of links for safety mechanisms and safety measures to be applied on hardware components. The hardware architecture shall be the perspective to collect the overall random failure information and link them to facilitate the calculation for the hardware architectural metrics and evaluation of the failure rate for violation of the safety goal. The hardware architecture is aimed to be based on the above hardware component net representation and shall be set on the top of EAST-ADL2.1.

#### Hardware Electronic Design

The Hardware Electronic Design represents the hardware detailed design as at the level of electrical schematics representing the interconnections between hardware parts composing the hardware components. The hardware electronic design is the perspective where the random failure information of the physical electronic part is available (including value for complex component such as microcontroller or ASIC). An unambiguous relation between hardware parts failure information and hardware components failure data shall be defined to permit the quantitative assessment of the hardware architecture level. The hardware electronic design is aimed to be based on the above hardware part net representation and shall be set on the top of AUTOSAR 4.0.

#### Hardware Software Interface

The concept for Hardware Software Interface (HIS), as specified in Part 4 for the product development at system level, shall be explicitly represented in the system architecture composed by hardware and software architecture. Therefore, EAST-ADL2.1 needs to be adjusted to support a clear separation of hardware and software with respective component behavior attached to the component. An explicit element interface between software function and hardware component needs to be defined. This concept shall support continuity of domain flow (e.g. software as sampled physical data and hardware as electrical data) for functional simulation and error propagation. In addition, it shall allow abstraction principle compared to detailed concrete implementation applied at the system level architecture.

#### Failure Rate and Failure Mode

Hardware failure information such as failure rate and failure mode shall be captured in an unambiguous formalism to enable the data exchanged within supplier chain and to facilitate quantitative assessment of the hardware architecture. Moreover, this concept shall support the allocation and interrelation between logical hardware component and physical hardware part for join calculations between hardware random failure from different hardware abstraction level (hardware architecture and hardware electronic design).

#### Fault and contribution to Safety Goal/Malfunction

The contribution of the hardware component to the violation of the safety goal shall allow tagging safety-related component. Although the item identified during hazard analysis can be decomposed according to sub-system development scenario. The hardware sub-system can only exhibits a local malfunction, and its contribution to the top level system malfunction linked to the violation of the safety goal. The relation to the top level malfunction, linked to the safety goal, of the local malfunction attached to a sub-part overall architecture, shall be incorporated in the meta model. The basic fault event of the occurrence of the top level malfunction, as hardware component fault, should be characterized by the type of fault (e.g. single point fault, latent fault, multiple or residual fault).

#### Hardware Metrics and Probabilistic value

Based on the hardware component faults, theirs relations for safety mechanism and associated coverage rate, the hardware architecture metrics (Single Point Fault and Latent Fault metric) need to be allocated first and subsequent verified by calculation. The same proceeding should be applied on probabilistic measures for the evaluation of safety goal violation due to random hardware failure (using Probabilistic Metric for random Hardware Failure PMHF) or for the evaluation of each cause using Failure Rate Class (FRC) method. The meta model extension developed in this work task shall enable to store the respective results of the calculation steps. Additionally, this provides

documentation of measures with their respective parameters or assumption. It shall also be able to express relation over the assumption of the logical hardware component and physical component part, to offer basic repository for the complete failure analysis methodology defined in WT3.3.1.

#### 4.2 Structure of document

The document is structured as follows:

Subsequent to the introduction an overview on the parts of ISO 26262, which are relevant for the hardware development with its relation and assessment to the system development, is given in section 5.

Within section 6, the interface with WT3.3.1 safety analysis methodology will be clarified and defined according to the analysis of the impact from the hardware abstraction view and representation (system, component, part) in 6.1, and to the definition of the element to be interfaced in 6.2.

The section 7 deals with the coverage of the hardware requirements from the initial ISO26262 standard analysis, with the description of the organization and the topics selected from this WT3.2.2 requirement analysis. Notice that initial and derived requirements are available in an external document traced from WT2.1 activities.

Section 8 deals with hardware modeling using EAST-ADL2 and AUTOSAR 4.0. On the one hand, the current version of EAST-ADL2.1 in particular for the hardware description is highlighted and described in 8.1. On the other hand in 8.2, some proposed extensions to this current version are explained which enhance the possibility to perform complete hardware components development and quantitative safety analysis. Moreover the ECU Resource Template of AUTOSAR R4.0 will be exhibited in 8.3 showing how to use it for hardware part modeling. In section 8.4 we will briefly discuss a proposal for change of existing constructs.

The contribution of WT 3.2.2 to the SAFE meta-model is described in section 9. As introduced in section 9.1 the organization of change request and extension is presented. Section 9.2 gives a detailed description of the proposed change request for the current EAST-ADL meta model regarding classes and links Our extension for EAST-ADL is described in section 9.3. Moreover, an example for the application of the meta-model for hardware modeling is presented in section 10.

In section 11 the preliminary relation between the hardware part elements as proposed in AUTOSAR R4.0 ECU Resource template and the existing construct of IP-XACT is proposed.

Finally, in section 12 a conclusion and discussion is given.

#### 5 Overview on ISO 26262

Within this section, an overview of the relevant parts of ISO 26262 with regard to hardware modeling and safety-related measures activities are given. The selection of the presented parts is based on the SAFE requirements elicited in WT 2.1 which are allocated to WT 3.2.2.

Addressing the development process of electric / electronic components for passenger cars, the ISO 26262 "Road vehicles – Functional safety" came into effect in November 2011. This standard introduces a safety lifecycle which "encompasses the principal safety activities during the concept phase, product development, production, operation, service and decommissioning" ([1], part 2, p.3). This can be seen as a guideline that demands a risk-based development approach with seamless traceability. In Figure 1 an overview on the different parts of ISO 26262 is given.

Figure 1: Overview on ISO 26262 (Relevant parts highlighted)

The relevant requirements for the hardware related development are mainly provided in ISO 26262:2011, Part 5 in "Product development at the Hardware Level". As a consequence of the exclusion from Part 5 chapter 10 "product integration and test" as a SAFE project decision, this chapter was considered as non relevant for this analysis. However, the Part 4 (Product development at System level) is strongly interlaced with respected to hardware development. Moreover, also in other parts, namely Part 7 (production and Operation), Part 8 (Supporting processes), and Part 9 (Automotive Safety Integrity Level (ASIL)-oriented and safety-oriented analyses) requirements are provided that affect directly or also indirectly the hardware development. In the following, an overview on the relevant aspects from the respective parts is given.

#### Part 4: Product Development – System Level

During this phase the development of the item from the system level perspective takes place. The process is based on the concept of a V-model. Starting point (on the upper left side) is the specification of the technical safety requirements which is followed by the development of the system architecture and the system design.

#### Safety mechanisms

During the system development the technical safety requirements specify the necessary safety mechanisms to define measure to detect and control the fault in the system, and their interactions with the system design in order to reach a safe state within a tolerant fault interval. The safety mechanism shall be specified to prevent latent or multiple point faults with consideration of the given architecture and in particular for the one implemented by hardware component.

#### System Design – Technical Safety concept

The system design shall implement the technical safety requirements by defining the technical capability of the intended hardware and software design with regard to the safety achievement. Measure to avoid systematic failure shall be introduced according to safety analysis in order to avoid system failure, via introducing of safety mechanism for component failure mitigation. According to analysis, specific measure to control random hardware failure during operation shall be specified. The target for the hardware architecture shall be defined according to architecture single point fault and latent-multiple fault, and for quantification of avoidance of the violation of safety goal due to random hardware failure.

#### System Design – Allocation to Hardware and Software

As introduce above the system design shall include the hardware and software partitioning via allocation of technical requirements.

#### System Design – Hardware Software Interface Specification

The interaction between hardware and software component shall be defined to allow specification of component hardware devices controlled by software. Additionally, hardware resources, configuration and error mechanism shall be specified.

#### System validation

The validation with hardware metrics for random hardware failure shall be carried out at the item via evaluation of criteria for the evaluation of safety goal violation due to random hardware failures and for architectural metrics as single point fault and latent-multiple fault metrics (calculation of results versus targets).

#### Part 5: Product Development – Hardware Level

During this phase the development of the item from the hardware perspective is performed. The process is again based on a V-model, going down with the specification of hardware safety requirements as well as hardware design and implementation.

#### Hardware Design

The hardware design shall be performed in accordance to system design and hardware safety requirements. It starts from the hardware architecture down to hardware detailed design at the level of electronics schematic describing parts interconnected. The traceability between hardware and safety requirement shall be traceable down to the lowest level. The environmental condition and potential cause of failure of hardware component shall be considered during design of hardware ware component.

#### Safety Analysis

The safety analysis on hardware design identifies the causes of failure and effect of faults in the overall system failure. The effectiveness of safety mechanism shall demonstrate to avoid single-

point fault, to maintain the system in safe sate and to validate coverage with respect residual and latent faults. This WT3.2.2 will not propose methodology for fault propagation and failure identification as this is includes in WT3.3.1, but will provide necessary element to describe the fault and safety constraints to the respective hardware components and hardware parts.

#### Evaluation of Hardware metrics

The hardware architectural metrics shall be computed to evaluate the effectiveness of the architecture to cope with random hardware failures. They have to be computed, for each violation of each safety goal on respective item of ASIL B to D, and to be applied iteratively from hardware architecture down to hardware design level. Similar to safety analysis, WT3.2.2 will only cope with the elements to capture component failure information, metrics targets and results for relation to failure of hardware parts.

#### Evaluation of safety goal violation due to random hardware failure

The evaluation of the residual risk of violation of safety goal due to random hardware failure due to single-point fault, residual faults and possible dual-point (multiple) faults shall be evaluated for each violation of each safety goal on respective item of ASIL B to D. Two methods can used either Probabilistic Metrics for random Hardware Failure (PMHF) which is build by a quantification of a fault tree analysis, or Failure Rate Class (FRC) method which basically evaluates each fault (single-point, latent ...) for each individual hardware component. Similar to safety analysis, WT3.2.2 will only cope with elements to capture component failure information, metrics target and results for relation to failure of hardware parts.

#### Part 7: Production and Operation

The relevant requirements for WT 3.2.2 arise from two sections of part 7, namely "Production" and "Operation Service". As for this product cycles the requirement encompasses largely the hardware development, only the requirement related to hardware safety measure initiated during hardware product development will be considered.

#### Part 8: Supporting Processes

The relevant requirements for WT 3.2.2 arise from Part 8 "Supporting processes", section 6 namely "Specification and management of safety requirements" and "Verification". Section 13 "Qualification of hardware component" is in focus of work task WT3.2.4.

#### Specification and Management of Safety Requirements

The objective of this section of ISO 26262 is to ensure that all safety requirements are specified correctly with respect to their attributes and characteristics. In addition the management of the safety requirements and tracing during the entire safety lifecycle has to be consistent, in particular for hardware development as context of this task.

#### Part 9: Automotive Safety Integrity Level (ASIL)-oriented and Safety-oriented Analyses

The relevant requirements for WT 3.2.2 arise from three sections of part 9 "Automotive safety integrity level (ASIL)-oriented and safety-oriented analyses", namely section 7 "Analysis of dependent Failures" and section 8 "Safety Analyses" as reference for hardware element as introduced in System Design part 4 and Hardware development part 5. The section 4 related to "Criteria for coexistence of elements" and section 5 related to "requirement decomposition with respect to ASIL tailoring" is ensured WT3.1.1. Therefore, only from the first two above sections an overview is given.

#### Analysis of Dependent Failure

The analysis of depended failures on the architecture induces to introduce specific measure to be applied to architecture element (e.g. such as redundancy, dissimilar development, safety mechanism, physical barrier, etc). A common cause failure and cascading analysis failures analysis shall

be performed for the architecture considering operational life of the product. This evaluation shall be performed on systematic fault, random hardware failure according to adequate required methods.

#### Safety Analyses

With the help of the safety analyses consequences of faults and failures on functions, behavior and design of items and elements shall be examined. The context of hardware element is targeted in this task. Moreover, the analyses provide information on causes and conditions that could lead to the violations of a safety goal or safety requirement.

#### 6 Safety Analysis Methods Interface

After presenting the relevant parts of ISO 26262 for hardware modeling and in addition to the primary goal of the representation of the Technical Safety Concept, the calculation of the hardware metrics and probabilistic value on hardware element shall be performed. It is essential that abstraction level of the hardware development is considered; meaning capability for separation of Hardware function and electronic component packaging during development and modeling. Furthermore, these models shall allow to perform safety analysis methods by first qualitative and then quantitative value for hardware element. It has been stated that the hardware package will include construct for hardware modeling, necessary constructs to perform quantitative measurement, such as failure mode and rate, and constructs to allocate or store results of the quantitative hardware analysis, such as Single Point Fault metric or Probabilistic Metric for random Hardware Failures.

The following chapter defines the boundary of the safety analysis methods interface, and interface element in detail.

#### 6.1 Interface Methodology for Safety Analysis

The model based methods to perform safety analysis, in particular on hardware design to the failure and effect of faults as defined in ISO 26262-9:2011-Clause 8, is defined in the context of WT3.3.1 formally work task "Safety Analysis". The outputs of an analysis per safety goal are: the identification of safety related attribute of the hardware component; the relation of the hardware component to the context of analysis as the safety goal or the sub-system malfunction in case of decomposition of the system; the typing of the elementary component fault as safe fault, singlepoint or residual fault and multiple-point latent; the identification of the safety mechanism covering the component fault. These outputs are required to enable the calculation of the hardware architecture metrics and the residual risk of violation of safety goal due to random hardware failure.

In addition the model-based development process foreseen by SAFE takes into account all the elements / attributes that potentially contribute to a safety risk on vehicle level. So, from vehicle items, all elements are decomposed according to engineering phase defined by the ISO26262 standard, being represented by the Functional Safety Concept and by the Technical Safety Concept. Then, according to the hardware development requirement from Part 5, the hardware architecture and detailed hardware design shall be captured to allow then further iterative safety analysis.

The architecture principle selected for the consideration of these needs is based on abstraction view and viewpoint, capable to capture and interconnect all relevant artifacts. The resulting architecture which is used is presented in the Figure 2.

| Operational<br>Perspective | Functional<br>Perspective | Variability<br>Perspective | Environment<br>Perspective | Logical<br>Perspective                | Technical<br>Perspective                                       | Geometrical<br>Perspective                   | ISO26262<br>view             | /         |

|----------------------------|---------------------------|----------------------------|----------------------------|---------------------------------------|----------------------------------------------------------------|----------------------------------------------|------------------------------|-----------|

|                            |                           | Syst .Feature              | Sys Design<br>Limit        | System Function<br>Block              |                                                                |                                              | Functional Safety<br>Concept |           |

|                            |                           | SW Feature                 |                            |                                       | Software architecture blocks                                   | Allocation                                   | <u> </u>                     | System    |

|                            |                           | HW Feature                 | Design Limit               |                                       | Hardware architecture blocks                                   | E/E wiring & In<br>ECU                       | Technical<br>Safety Concept  | Sys       |

|                            |                           | SysC. Feature              |                            |                                       | SysC. architecture blocks                                      | Hydraulic,<br>others                         |                              |           |

|                            |                           |                            |                            | Software<br>component<br>architecture | Software component<br>design allocation (RTE<br>configuration) | Core<br>Allocation                           |                              |           |

|                            |                           |                            |                            | Hardware<br>component<br>architecture | Hardware component<br>design allocation<br>(package)           | PCB<br>Allocation                            | /                            | Component |

|                            |                           |                            |                            | Systems<br>component<br>architecture  | Systems component<br>design allocation (Meca.<br>package)      | Physica<br>Flow (as<br>Hydraulic,<br>others) |                              | Com       |

|                            | Requireme                 |                            | ·                          | Architectu                            | ire and Design Support                                         |                                              | Safety<br>Support            |           |

Figure 2: Overview on structure of architecture (Relevant parts highlighted)

As introduced in task description, the hardware description is mapped to the existing language EAST-ADL. The EAST-ADL is structuring functional decomposition and architectural element definition in the Design abstraction view of EAST-ADL and the Implementation view AUTOSAR. The mapping of view point for hardware development in accordance to Figure 2 is conform to

- Hardware architecture is represented by EAST-ADL Hardware Design Architecture

- Hardware detailed design is represented by AUTOSAR HW Element from ECU Resource Template

It can be noticed that as Hardware Design Architecture of EAST-ADL is also capable to represent Hardware Detailed Design, methods proposed shall allow the support of compatible interface required by Safety Analysis.

Finally, the safety analysis analyzing hardware component failure and identifying their fault classification (single-point or residual...) shall be visible at the hardware architecture level. This iterative process of failure analysis allows to iteratively introduce safety mechanism and mitigation effect, and to validate their impact and efficiency. The process is not intended to be detailed here, but simply showing that hardware architecture will evolve according to safety analysis and technical safety requirement management and refinement. The Figure 3 below, represent a general overview of the iterative process that will be considered in WT3.3.1 according concrete method selection.

The given assumption for WT3.2.2 is that component fault characterization, the safety related component tag and the relation of the component to the safety/malfunction is given from this safety analysis. In addition this analysis is also built on the top of the hardware architecture composed of hardware element and hardware safety mechanism, the traceability of safety mechanism to the component fault mitigates, and finally by the fault propagation methodology.

- Step 2: Tag of each block safety contribution (function, diagnosis, mechanism...)

- Step 3: Generation of propagation for Qualitative analysis (FTA)

Deductive methods : FTA: Fault Tree Analysis Inductive Methods : FMEA: Failure Mode and Effect Analysis / FMEDA : Failure Mode, Effect and Diagnosis Analysis

#### Figure 3: Overview on iterative safety analysis methods

Moreover, the hardware development process may then, depending of industrial process, perform allocation of Hardware Component in Hardware Part in consideration of electronic industrial process (e.g. see example in Figure 4 below). Such separation of concern shall then consider the inter-relation between fault characteristic at architecture level and origin from fault at design level.

#### Figure 4: Hardware allocation and quantitative analysis

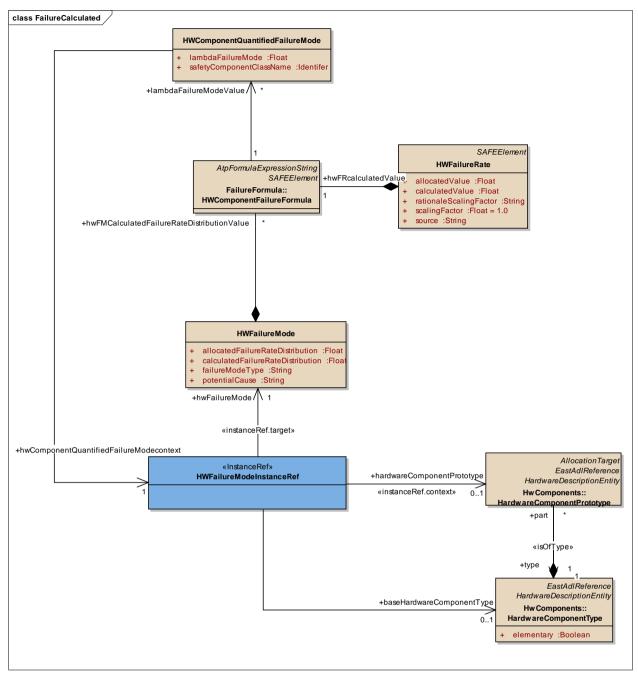

So, the safety analysis is performed on the impact analysis of the failure mode of the Hardware Component. In the context of the architecture, the hardware components are tagged as safety related and its failures modes are characterized as safe fault, single-point or residual fault and multiple-point latent fault. The corresponding failure modes of the hardware component are considered as malfunction for the electronic design. The quantitative values are computed from this fault consideration and from the diagnostic coverage of hardware element identified as safety mechanism. Such measures are the hardware architectural metrics as Single-Point Fault metric or Multiple Point-Fault and Latent metric, plus the Probabilistic Metrics for random Hardware Failure or the individual Failure Rate Class evaluation.

The necessary failure rate and distribution, only available at the hardware part level, shall then be combining to retrieve computed failure rate at the architecture level for each failure mode of the hardware component considered. The correspondence will be performed by the quantification of the hardware component malfunction. SAFE meta model constructs shall allow to store this different failure information and calculation relation using self define formula. It shall also permit to define target values and store results of the quantitative hardware analysis. We propose to store in constructs by WT3.2.2: the definition of formula for quantitative measurement as relevant failure information is store in modeling element. From this interface defined in WT3.2.2, the tools and methods specification of WT3.3.1 as D3.3.1.b deliverable will validate the initial formula for calculation on the top of actual information provided in this chapter and related SAFE model element in chapter 9.3. Moreover WT3.3.3 as architecture benchmark analysis makes use failure and metric, and will provide a context for validation (see specification D3.3.3[8])

#### Key Steps of Hardware modeling and analysis

Based on the considerations described above the key steps of the methodology for hardware modeling and safety analysis can be formulated as below, and shall consider assumption for WT3.3.1 work task in the overall detailed methodology. The key steps are identified as:

- Capture Hardware Technical Safety Concept (with Hardware Component)

- Complete Hardware Component Failure Propagation (Iterative process for Safety Mechanism validation)

- Define (or Reuse) initial failure rate data for hardware components and calculates metrics

- Define Hardware Component allocation and Malfunction (from Hardware Component into complex parts such as ASIC, FPGA)

- Develop Electronics Schematic and capture (or reuse existing) Hardware Part

- Perform/Reuse Electronic part detailed failure analysis (e.g. FMEA) and contribution to Hardware component malfunction

- Verify hardware component Metrics and Probabilistic value

#### 6.2 Interface Element

The split decided in the work task organization between safety analysis methods from WT3.3.1 and hardware meta model from WT3.2.2, was that, in addition to hardware component and hardware part, the SAFE construct for hardware modeling will include: hardware failure related information, calculation constructs necessary for hardware architectural metrics and for the two methods for evaluation of the residual risk for violation of the safety goal.

Moreover, constructs shall provide the relationship of the formula calculation for computation of Hardware Component failure rates from Hardware Part failure rate and distribution value from industry source).

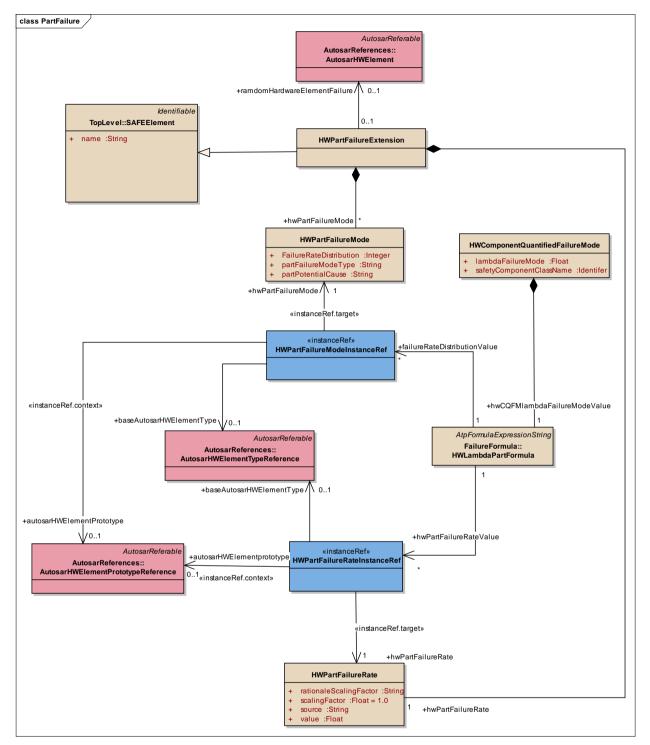

The list of artifacts, consolidated by WT2.1 analysis and derivation requirement synthesize in 7, is initiate from following concept:

- Failure Mode, Failure Rate and Distribution for Hardware Part (to be imported from industry source)

- Failure Mode and Failure Rate of Hardware Component

- Fault Enumeration to allow Failure Mode characterization of a Hardware Component in the type in context of an overall hardware architecture

- Identification of Safety Related impact of the Hardware Component

- Formula to provide relation and perform calculation from Hardware Part to Hardware Component in the context of an electronic design and the given hardware malfunction for the design element

- Hardware architectural metric target values and results for Single-Point Fault Metric and Latent-Fault Metric

- Probabilistic Metrics for random Hardware Failure (today simplified approach) target values and results

- Failure Rate Class target values , values for each Hardware Component and defined measures

- Formula to perform calculation required for architectural metrics, probabilistic metrics and failure rate class, depending of Hardware Component Failure Rate, potential Diagnostic Coverage of the selected Safety Mechanism

- Relation to the top level malfunction (linked to the Safety Goal of the item) of the hardware architecture, to allow evaluation for each Safety Goal (direct or indirect evaluation)

The concrete details of the meta model elements is defined in section 9.3.

Notice that as defined in previous section, thanks to the expressiveness of Hardware Design Architecture from EAST-ADL capable to represent Hardware Detailed Design, the constructs provided could allow completing the calculation directly from Hardware Component model, and so preventing using elements of Hardware Part if convenient.

#### 7 Hardware modeling scoping

In the work of WT2.1 the ISO 26262 was analyzed into detail. Requirements were elicited from each part of the standard and textually described with the corresponding ISO references. For WT3.2.2 - hardware modeling – requirements out of part 4, 6, 7, 8, 9 and in particularly Part 5 had to be considered. Derived work task specific requirements describe all necessary characteristics for the meta model extension of WT3.2.2, to provide hardware modeling on hardware architecture level and detailed level of hardware electronic design for hardware safety evaluation. To provide structure and traceability in managing the work task specific requirements, the relevant ones were categorized by their impact on the hardware model for the SAFE meta models extension. Based on the requirements elicitation five categories were derived and introduced: requirements for hardware components, hardware failures, hardware modeling regarding meta model constructs is to provide all necessary information for structural and failure description of hardware components as well as constructs for the evaluation of hardware with regard to hardware architectural metrics and evaluation of safety goal violation according to ISO 26262 Part 5, Clause 8 and 9.

The presented categories contain all requirements for SAFE meta model extension and are explained into detail in the next sections. Please notice that the refined requirements are not reported below, as these categories where build to provide an initial structure for the SAFE meta model contribution as detailed in section 7.6.

#### 7.1 Requirements Package: Hardware Components

Requirements regarding the structure of hardware components and parts for hardware architecture and hardware electronic design were collected in the category hardware component. To facilitate safety evaluation of a hardware design, the hardware components and their interference have to be described into detail according to the needs in ISO 26262, Part 5. The requirements for hardware component structure are partially related with existing EAST-ADL and AUTOSAR constructs. As the requirement collected for Design Environmental Condition and Special Characteristics deals with constraints description for design operation and then production, operation, decommissioning and maintenance, they can be express through Requirement EAST-ADL constructs and so are not considered in additional meta modeling artifacts.

The package hardware component addresses the description of hardware components and parts as well as composition of components or parts including port and pin connections. Hardware/Software-Interfaces facilitate the presentation of hardware which is controlled by software. The representation of elementary hardware components and the categorization of hardware components are also included.

#### 7.2 Requirements Package: Hardware Failure

The category hardware failure groups all requirements of the ISO 26262 regarding the relevant failure description of hardware components and parts. A meta model extension for the failure description is related to capture all requirements.

The package hardware failure captures the description of different failure modes and a failure rate of hardware components and parts including potential causes of the failure mode, the failure rate distribution of the failure mode and contribution to the malfunction (linked to violation of a safety goal). Safety mechanisms with their diagnostic coverage are also addressed.

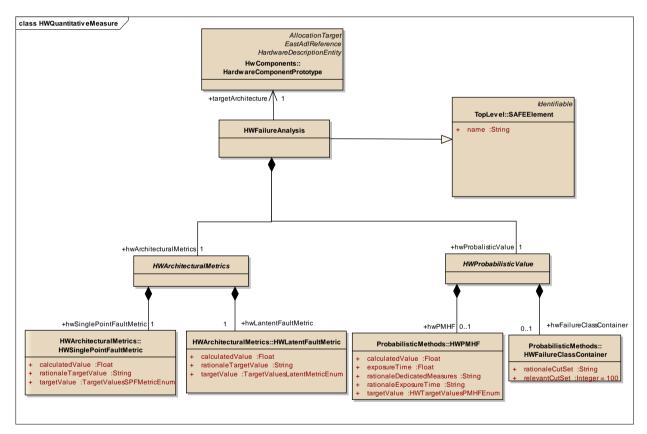

#### 7.3 Requirements Package: Hardware Architectural Metrics

The hardware architectural metrics, described in ISO 26262 Part 5 Clause 8, provide the first safety evaluation of the hardware architecture claimed by the ISO. All requirements to perform this evaluation as well as the methodology, calculation and results are collected in this requirements package.

The package hardware architectural metrics captures the single contribution of each violating failure mode as a specific failure rate, according to its characterization. Target values for the architectural metrics are provided.

#### 7.4 Requirements Package: Safety Goal Violation

The evaluation of residual risk of safety goal violation is the second safety evaluation claimed by the ISO 26262 and is described into detail in Part 5 Clause 9. All requirements which are relevant for both methods, the *Probabilistic Metric for Random Hardware Failure* (PMHF) and the *Failure Rate Class* (FRC) approach, are grouped in this category.

This requirement packages addresses all necessary calculations for the evaluation of safety goal violation as well as target values. Exposure time for dual-point faults and required dedicated measures are included. Additionally, diagnostic coverage on hardware component level are described.

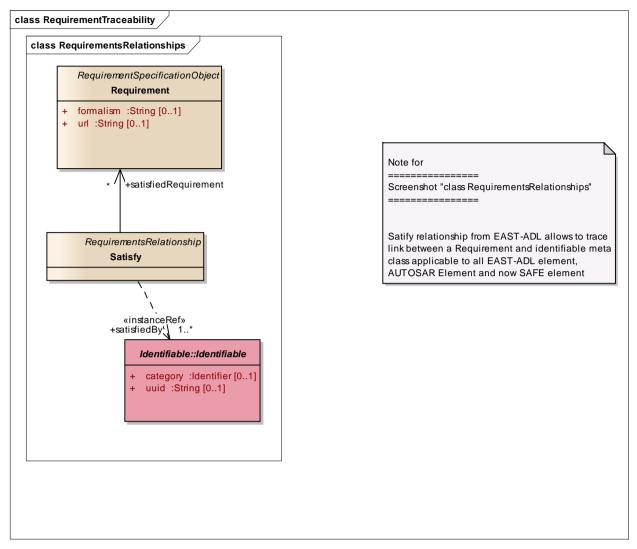

#### 7.5 Requirements Package: Traceability

The traceability of safety requirements such as safety goals regarding the evaluation of the hardware architecture is provided by the requirements in the category traceability. These requirements are in focus work task WT3.1.2 for the "Safety Requirement Expression".

The package traceability addresses the dependency of technical and functional requirements. Additionally, the links of hardware components to hardware safety requirements and the traceability from a preliminary design to hardware components at electronic level are captured.

#### 7.6 Allocation of the requirements packages to derived meta model structure

A structure for the meta model was derived from the structure of the requirements categorization. Therefore, the meta model contains the following sub-packages in the package *Hardware*:

- Sub-Package *Structure*, according to the requirements category hardware components as change request for EAST-ADL and AUTOSAR

- Sub-Package *Failure*, according to the requirements category hardware failure

- Sub-Package *HWQuantitativeMeasure* for the classification of the assessments to the architectural metrics or probabilistic methods for hardware safety evaluation. Additionally, the quantitative assessment for the calculation of single contribution for each failure mode is included.

- Sub-Package *HWArchitecturalMetrics*, according to the requirements category Hardware Architectural Metrics

- Sub-Package *ProbabilisticMethods*, according to the requirements category Safety Goal Violation

- Sub-Package *Traceability*, according to the requirements category Traceability mainly reusing existing artifacts from EAST-ADL

• An additionally package *FailureFormula* contains all formula expressions required for the evaluation of hardware. This has to include the quantitative measures and the previous calculations exemplarily, of the single failure mode contributions.

In this section the current status of the architecture description language EAST-ADL regarding hardware is described. Based on the investigation a proposal for adaption and extension of existing constructs is provided to facilitate an evaluation of detailed hardware architectures regarding functional safety in accordance with ISO 26262.

#### 8.1 Current status of EAST-ADL

EAST-ADL provides the description of an automotive architecture on different levels of abstraction. This namely is the vehicle level, analysis level, design level, implementation and operational level. This architecture description language was developed in various projects together with Original Equipment Manufacturers (OEMs), suppliers and research institutes. Current published version of EAST-ADL is version 2.1, see also <u>www.east-adl.info</u>.

The class diagram *PackageDependencies* of EAST-ADL V2.1[5] gives an overview of the dependencies of the package and is presented in Figure 5. Beside the described abstraction layers, especially the sub-package *HardwareModeling* and the package *Dependability* are in special interest for hardware and failure modeling. This has to be related with the hardware evaluation including the architectural metrics and the probabilistic methods.

Figure 5: Class diagram for Package Dependencies

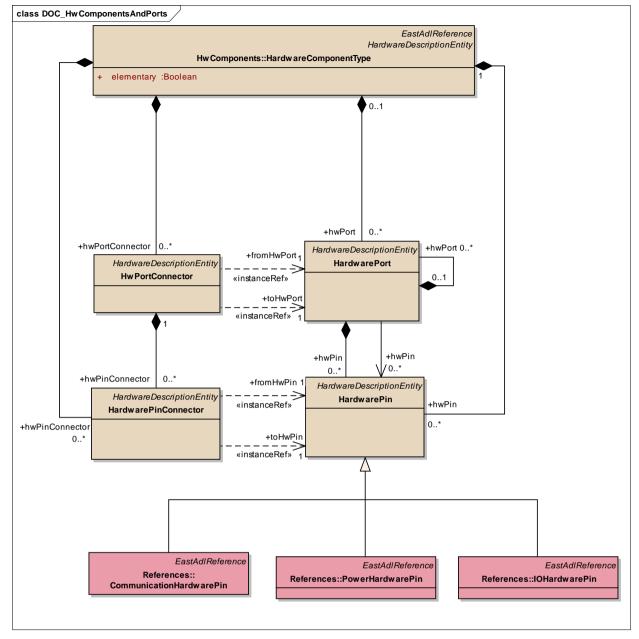

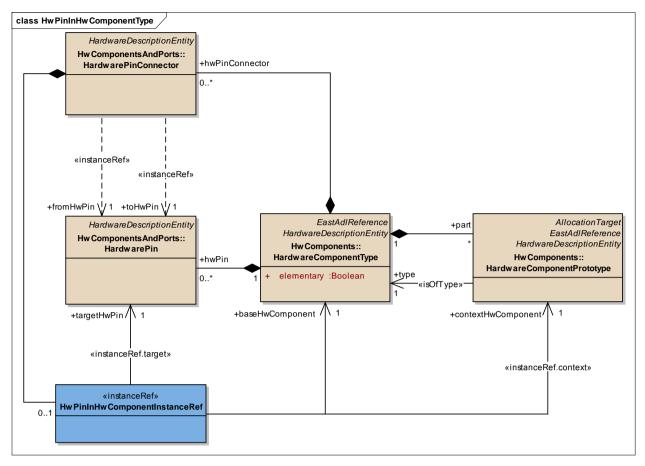

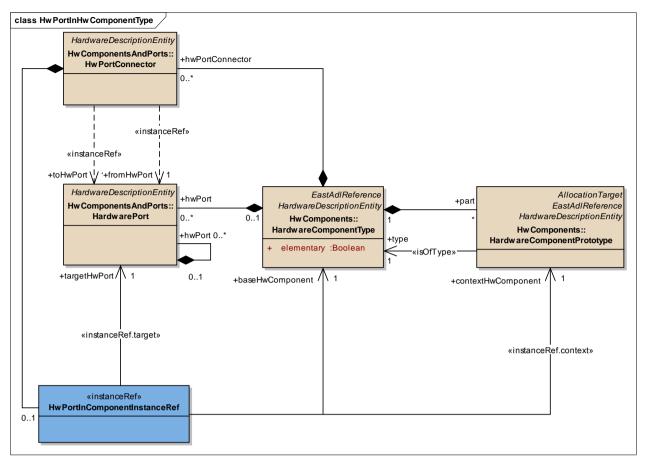

In the sub-package *HardwareModeling* of the package *Structure*, EAST-ADL V2.1 describes the hardware modeling in the corresponding diagram. The construct HardwareComponentType and HardwarComponentPrototype provides a structural entity that defines a part of an electrical architecture [5], as shown in Figure 5. Further class of interest are the *HardwareConnector*,

HardwarePin and HardwarePinGroup, as the can be used for the description of the electrically connection of hardware components regarding their logical bus between ports of the hardware component.

Figure 6: Class diagram for Hardware Modeling in the EAST-ADL2

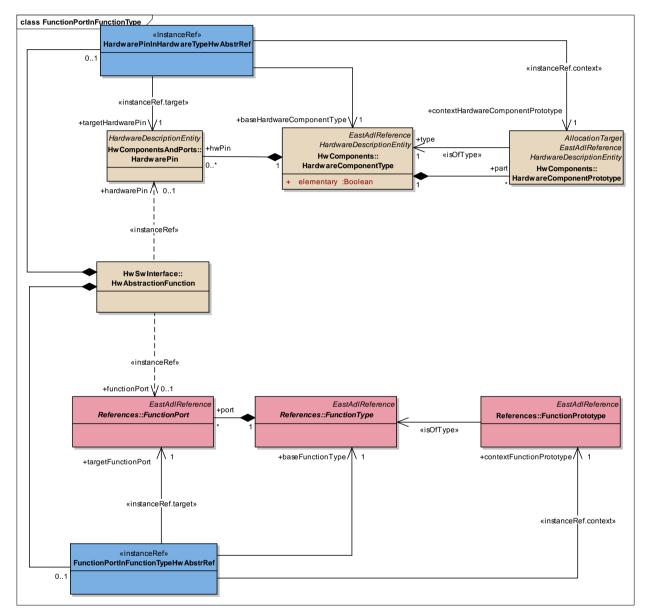

The proposed use of hardware construct HardwareComponentType in Design Level of EAST-ADL2.1 methodology is to build the hardware node and topology including sensors and actuators, define the allocation of functional block as DesignFunctionType. Notice that the to HardwareComponentType allows further decomposition to be able to decompose an ECU node. But the DesignFunctionType can be specialized, as visible in the Figure 7, as hardware via HardwareFunctionType or software with DesignFunctionType or LocalDeviceManager to interface a Sensor or BasicSoftwareFunctionType as a general basic software module. Moreover, the behavior of the function FunctionBehavior is associated to the FunctionType. So the top level FunctionType represent functional chain of hardware and software element. as DesignFunctionType, where HardwareComponentType are simply a container, via allocation link, for HardwareFunctionType. So the use of Design Level is still a functional approach, as software and hardware and not completely split.

Figure 7: Class diagram for Function Modeling in the EAST-ADL2

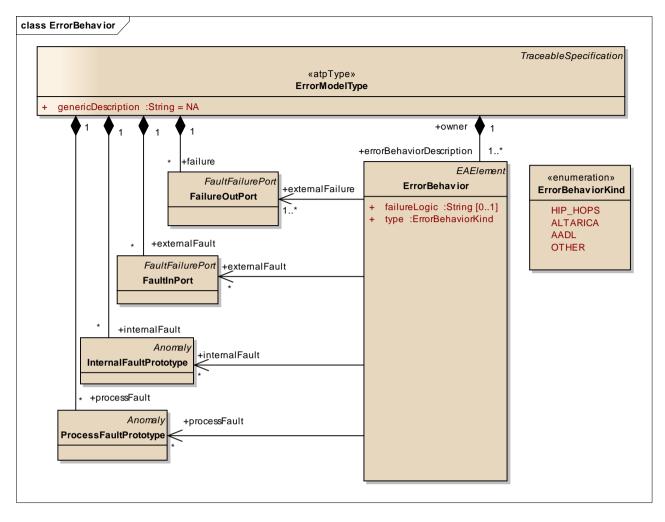

Then for the failure part, in the sub-package *ErrorModel* of the package *Dependability*, EAST-ADL2.1 describes the error modeling in the corresponding diagram, as shown in Figure 8. Propagation points for faults can be described by the class *FaultInPort* and *FailureOutPort*, while the *FaultFailurePort* describes an abstract port for faults and failures and depends on a hardware pin. The constructs *ErrorModelType* and *ErrorModelPrototype* provides a hierarchical composition of error models. The connection of the *ErrorModel* with the structural element *FunctionType* and *HardwareComponentType* is made via respective allocation link as *errorModelPrototype\_hwTarget* for *HardwareComponentPrototype* and *errorModelPrototype\_functionTarget* for *DesignFunctionPrototype* (with relevant specialization from Figure 7).

A typical target of the *ErrorModelType* is exemplarily a system/subsystem, a function or a hardware device and represents the internal faults and the fault propagation of the targeted element. From the EAST-ADL2.1 Design Level modeling methodology, as introduce above, the functional approach applied to *ErrorModel* for safety analysis constraints the use of *ErrorModel* for *HardwareComponent* to describe hardware fault that propagates Failure to *DesignFunction* (hardware or software functional behavior) as a hardware resource failure. The signal fault propagation is supported by the *ErrorModel* of *HardwareFunctionTyp*e. In the physical electrical domain this split of concern is not visible.

Figure 8: Class diagram for Error Modeling in the EAST-ADL2 Dependability

In the sub-package *ErrorModel* of the package *Dependability* EAST-ADL 2.1, describes the error behavior in the corresponding class diagram *ErrorBehavior*, as shown in Figure 9. The presented different faults can have the following different roles: external, internal or process faults. While class *FailureOutPort* and *FaultInPort* represent the described propagation points, the *InternalFaultPrototype* represents an internal condition of the target that concerns the components faults/failure definition.

For the stake of fault of hardware part, the internal fault as InternalFaultPrototype represents the failure mode of the HardwareComponent. The others relevant information for quantitative assessment as failure rate and distribution are not clearly defined. construct А QuantitativeSafetyConstrainst is present but only associate to a FaultFailure as an instance reference of an Anomaly, as the top level failure effect of an ErrorModel as typed FailureOutPort.

Figure 9: Class diagram for Error Behavior in the EAST-ADL2 Dependability

#### 8.2 Proposed extensions to EAST-ADL

Basic constructs needed for structural description of hardware exists in EAST-ADL V2.1, as shown in Figure 6. With regard to the elicited requirements of ISO 26262 these concepts and constructs can cover and fulfill high level description of hardware node and sensors/actuators. Inconveniences exist for the interconnection of hardware components on the abstraction of low level electronics. To model hardware architectures on detailed level to perform the demanded metrics, constructs for the structural description has to be provided, exemplarily for hardware ports, pin and their specific connectors. Additionally, a Hardware-Software-Interface (HSI) has to be introduced, claimed by the ISO 26262. Therefore, an adaption of the structural part for the hardware modeling has to be provided. Existing artifacts in EAST-ADL shall be referenced and linked, as it should be objective to reuse as much as possible of the existing structural constructs for the SAFE meta model extension. We propose for the structural part a change request of EAST-ADL. The corresponding meta model adaption is presented in Section 9.2.

Beside the structural part, the specific requirements for hardware modeling presented in Section 7 claim the description of hardware failure information and the metrics for qualitative and quantitative analysis. Beside the concepts for error modeling with the definition of propagation points the EAST-ADL V2.1 provides no constructs for failure information. To provide failure modes, failure rates of hardware components etc. the existing constructs have to be extended. For the qualitative

and quantitative assessment of the hardware failure expressions have to be formulate and constructs for storage of the results,

These potential extensions together with their rational are described in the Section 9.3. However, as this task is still going on in future also the potential extensions will be elaborated in more detail.

#### 8.3 Current status of AUTOSAR

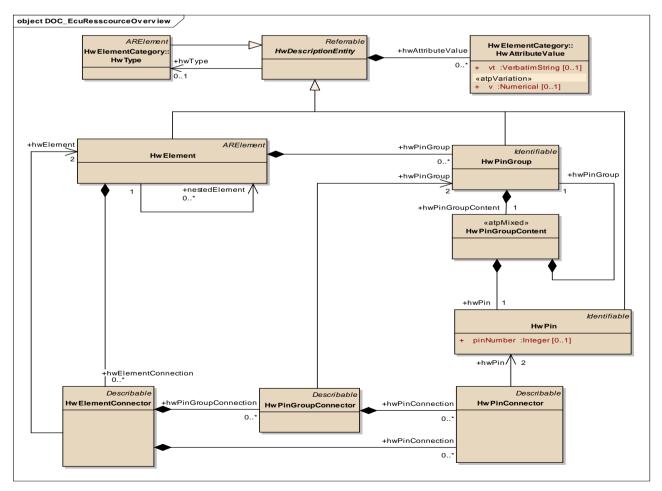

As proposed by EAST-ADL abstraction view, AUTOSAR provides the implementation view that represents the software oriented implementation. For the hardware related part, in particular in AUTOSAR the ECU Resource Template, main elements capable to represent hardware design element are available. As it is depicted in Figure 10, the basic class *HwElement* exists. This element can be composed of *HwPin* through the intermediate class *HwPinGroup*. Then a connector can connect two *HWElement* by a *HwElementConnector* and then connect *HwPin* via *HwPinConnector* or *HwPinGroup* via *HwPinGroupConnector*.

So, we can represent a nested composition like of *HwElement* by using the *nestedElement* relationship, knowing that in term of semantic this is not a strict composition.

By such means an ECU can be defined as nested *HwElement*, connected together by their *HwPin*, *HwPinGroup*, to represent all the electronics Hardware Part and to define a complete ECU electronic schematic as hardware electronic design level. As explain in the next section, there is place for improvement in order to align concept with HW Component and compositional organization of an ECU organization.

Figure 10: AUTOSAR ECU Resource overview

#### 8.4 Proposed extensions to AUTOSAR

As Introduced in the previous section, to facilitate hardware part representation and compositional aspects, the ECU resource template requires some improvement. Due to AUTOSAR IPs, we will only express needs and then propose to submit this subject to the AUTOSAR consortium as a potential improvement area for a future official change request.

The draft of the main features to be change in ECU Resource template is the introduction of compositional capability by the creation of HwElementType composed of part from *HwElementPrototype*. Another possible of change would be to revise *HwPinGroup* definition in order to introduce the concept of Bus, in order to be more restrictive in the *HwPin* composition.

#### 9 WT 3.2.2 Contribution to SAFE Meta-Model

Within this section the contribution of WT 3.2.2 to the SAFE meta-model is described. At the beginning an overview about the model is given which is followed by the detailed description of the classes and interconnections. Moreover, in another section the meta-model is described by means of an example.

#### 9.1 Overview

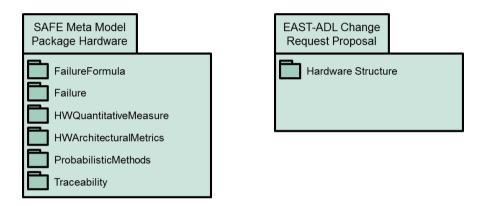

The structuring of the meta model extension regarding hardware is done according to the categories defined in Section 7.6 as shown in Figure 11.

The top-level package *Hardware* of the SAFE meta model, developed in Enterprise Architect, contains all meta model extension of WT 3.2.2, except for the structural part. The meta model adaption for EAST-ADL capturing the structural part is described in Section 9.2, as the decided choice was to shift it away from the package *Hardware* and make proposal for EAST-ADL2.1 adaptation in *HarwdareStructure*.

The package *Hardware* with its sub-packages FailureFormula, Failure, HWQuantitativeMeasure, HWArchitecturelMetrics, ProbabilisticMethods and Traceability is described in Section 9.3.

Due to the fact, that the meta model regarding hardware is partially based on the existing constructs of EAST-ADL, a lot of references are included. Figure 12 gives an overview of the references to EAST-ADL which are used in the package Hardware. In case of a reference, all attributes from the EAST-ADL class are inherited. For some classes of EAST-ADL adaptations are required, described in Section 9.2.

Figure 12: References of package Hardware to EAST-ADL

#### 9.2 **Proposal for change request on EAST-ADL**

This following section will describe the details of the proposal for change request in EAST-ADL2.1. It covers the core feature of EAST-ADL in the structural part of the hardware element.

The first main change represents the introduction of the *HardwarePort*, for substitution on the long run the *LogicalBus* meta class. This *HardwarePort* can then be composed by *HardwarePin*, and *HardwarePort* will represent a transactional description of internal or external bus communication, similar to a concept available in IP-XACT (and in AUTOSAR *HwPinGroup*). As a consequence the *HardwareConnector* will be revised (see next section for details). Linked by the *HardwarePin* or any other hardware elements need to more flexible expressed. Our proposal is to reuse the *HwCategory* modeling concept from AUTOSAR (see next section and in AUTOSAR document for more details)

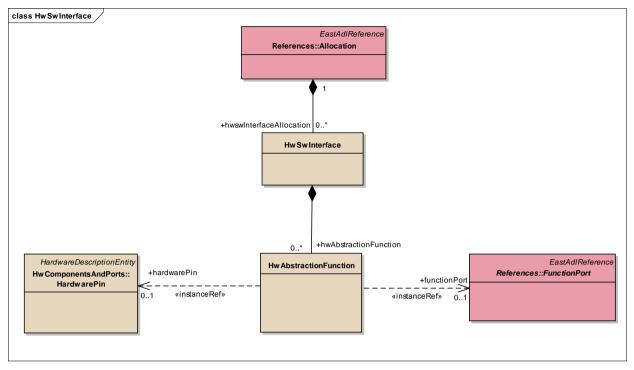

The second important change is the creation of the means for a separation at the Design level between hardware and software elements, as required by the ISO26262 requirement. The software architectural element could I be represent by design function (*DesignFunctionType*) and the hardware architectural element by hardware component (*HWComponentType*). As consequence, first a dedicated element shall be added to represent the hardware software interface, a *HwSwInterface* element representing the hardware abstraction (*HWAbstractionFunction*). Moreover them to complete the split, a behavior of the HW component shall be directly attached (*FunctionBehavior*), similar to the behavioral that is attached to *DesignFunction*. For example in hardware domain these behavior may be link to SystemC modeling element including the hardware behavior description for simulation capabilities.

In the following subsections, the detailed description of the classes and interconnections is detailed. Name of the top-level package is "Hardware Structure". This on the other hand contains 6 sub-packages, as following

- HwCategory

- HwComponentBehavior

- HwComponent

- HwComponentsAndPorts

- HwSwInterface

- \_instanceRef

#### 9.2.1 Package Hardware Structure

#### Package Notes:

This package describes the Change Request proposal for the original EAST-ADL package HardwareModeling

The package HardwareModeling contains the elements to model physical entities of the embedded electrical/electronic system. These elements allow the hardware to be captured in sufficient detail to allow preliminary functional allocation decisions. It also allow to define the hardware architecture description based on hardware component and associated behavior.

Conversely, the Functional Analysis Architecture and the Functional Design Architecture may be revised based on analysis using information from the Hardware Design Architecture. An example is control law design, where algorithms may be modified for expected computational and communication delays and then finally attached to hardware component. Thus, the Hardware Design Architecture contains information about properties in order to support, e.g., timing analysis and performance in these respects. Finally, it includes behavioral description of the control law when decision for hardware implementation is made.

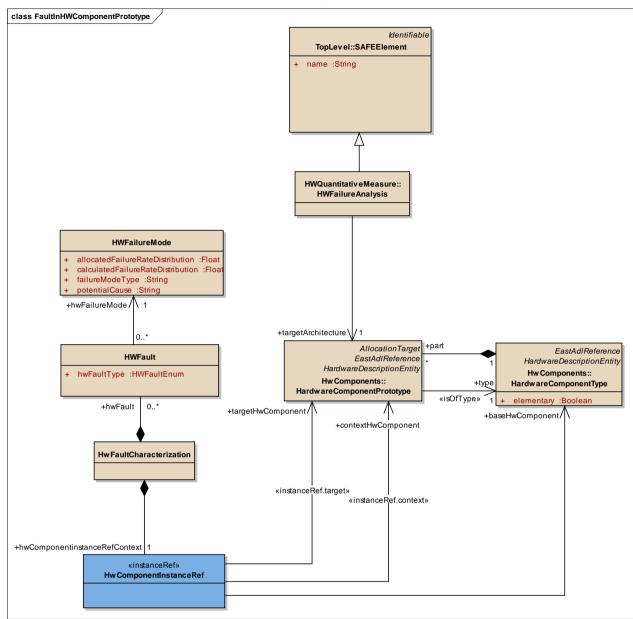

Figure 1: <u>HardwareModeling</u> - (*Class diagram*)

Diagram Notes:

This diagram shows an overview of the basic element of HardwareModeling as HardwareComponentType and HardwareComponentPrototype.

It also depicts the conservation of LogicalBus for backward compatibility. It is now proposed to be replaced by a more flexible concept the HardwarePort.

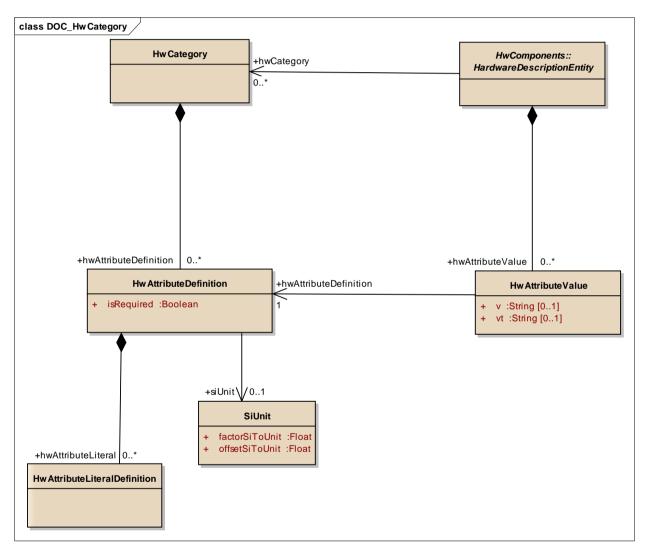

| 9.2.1.1 | Package HwCategory |  |  |

|---------|--------------------|--|--|

#### Package Notes:

This package represents the HwCategory, similar use as in AUTOSAR, to allow definition of specific attributes to all hardware entities of the Hardware Structure package.

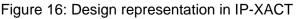

Figure 2: <u>DOC\_HwCategory</u> - (Class diagram)

#### Diagram Notes:

This class diagram represents a flexible definition of attributes, attached to any hardware entity of the Hardware Structure package, using meta-class generalization HardwareDescriptionEntity. This modeling style is the same as the one in use in AUTOSAR to facilitate reuse, refinement and linkage of element between EAST-ADL and AUTOSAR.

#### 9.2.1.1.1 Class HwAttributeDefinition

Element Base Classes:

Element Notes:

This HwAttributeDefinition class represents the ability to define a particular hardware attribute.

The category of this element defines the type of the attribute value. If the category defined by HwAttributeValue is Enumeration the hwAttributeEnumerationLiterals specify the available literals.

Semantic:

none

#### **Connections**

| Connector             | Source                       | Target                |

|-----------------------|------------------------------|-----------------------|

| Association           | HwAttributeDefinition        | SiUnit                |

| Source -> Destination |                              |                       |

| Aggregation           | HwAttributeDefinition        | HwCategory            |

| Source -> Destination |                              |                       |

| Association           | HwAttributeValue             | HwAttributeDefinition |

| Source -> Destination |                              |                       |

| Aggregation           | HwAttributeLiteralDefinition | HwAttributeDefinition |

| Source -> Destination |                              |                       |

#### <u>Attributes</u>

| Attribute  | Notes                                                          | Default |

|------------|----------------------------------------------------------------|---------|

| isRequired | This attribute specifies if the defined attribute value is re- |         |

| Boolean    | quired to be provided.                                         |         |

#### 9.2.1.1.2 <u>Class</u> HwAttributeLiteralDefinition

#### Element Base Classes:

Element Notes:

This HwAttributeLiteralDefinition play the role of HwAttributeLiteral for HwAttributeDefinition as the definition of the Enumeration. It is only applicable if the category of the HwAttributeDefinition equals Enumeration.

Semantic:

None

Connections

| Connector   | Source                       | Target                |

|-------------|------------------------------|-----------------------|

| Aggregation | HwAttributeLiteralDefinition | HwAttributeDefinition |

| Connector             | Source | Target |

|-----------------------|--------|--------|

| Source -> Destination |        |        |

#### 9.2.1.1.3 Class HwAttributeValue

Element Base Classes:

#### Element Notes:

This HwAttributeValue class represents the ability to assign a hardware attribute value. Note that v and vt are mutually exclusive.

#### **Connections**

| Connector             | Source           | Target                     |

|-----------------------|------------------|----------------------------|

| Aggregation           | HwAttributeValue | HardwarePort               |

| Source -> Destination |                  |                            |

| Aggregation           | HwAttributeValue | HardwarePin                |

| Source -> Destination |                  |                            |

| Aggregation           | HwAttributeValue | HardwareDescriptionEntity  |

| Source -> Destination |                  |                            |

| Aggregation           | HwAttributeValue | HardwareComponentPrototype |

| Source -> Destination |                  |                            |

| Association           | HwAttributeValue | HwAttributeDefinition      |

| Source -> Destination |                  |                            |

#### <u>Attributes</u>

| Attribute | Notes                                                 | Default |

|-----------|-------------------------------------------------------|---------|

| v         | This represents a textual hardware attribute value.   |         |

| String    |                                                       |         |

| vt        | This represents a numerical hardware attribute value. |         |

| String    |                                                       |         |

#### 9.2.1.1.4 <u>Class</u> HwCategory

#### Element Base Classes:

Element Notes:

This HwCategory class represents the ability to declare hardware category and its particular attribute. This Category can be associated to any HardwareDescriptionEntity, in particular to HardwarePin to define electrical characteristics, to HardwarePort to define communication parameter (e.g. speeds...), to HardwarePinConnector to define electrical feature (e.g. resistance) or to HardwarePortConnector (e.g. bandwidth or any limitation).

In addition, this construct can be attached to any HardwareComponent for further characteristic description (e.g. technology, etc...).

The decision for introduction of this element was to introduce a flexible definition of parameter for any hardware entity, and to move the parameter definition closer to AUTOSAR modeling style (to be reused or propagated between abstraction view).

Semantic:

none

| <u>Connections</u>    |                           |            |  |

|-----------------------|---------------------------|------------|--|

| Connector             | Source                    | Target     |  |

| Association           | HardwarePort              | HwCategory |  |

| Source -> Destination |                           |            |  |

| Aggregation           | HwAttributeDefinition     | HwCategory |  |

| Source -> Destination |                           |            |  |

| <b>Association</b>    | HardwareDescriptionEntity | HwCategory |  |

| Source -> Destination |                           |            |  |

| Association           | HardwarePin               | HwCategory |  |

| Source -> Destination |                           |            |  |

| Association           | HardwareComponentType     | HwCategory |  |

| Source -> Destination |                           |            |  |

#### 9.2.1.1.5 <u>Class</u> SiUnit

#### Element Base Classes:

Element Notes:

This is SiUnit class represent the physical measurement unit. All units that might be defined should stem from SI units. In order to convert one unit into another factor and offset are defined. For the calculation from SI-unit to the defined unit the factor (factorSiToUnit) and the offset (offsetSiToUnit) are applied:

Unit = siUnit \* factorSiToUnit + offsetSiToUnit

For the calculation from a unit to SI-unit the reciprocal of the factor (factorSiToUnit) and the negation of the offset (offsetSiToUnit) are applied:

SiUnit = (unit - offsetSiToUnit) / factorSiToUnit

Semantic:

Defined by SiUnit.

| <u>Connections</u>    |                       |        |  |

|-----------------------|-----------------------|--------|--|

| Connector             | Source                | Target |  |

| Association           | HwAttributeDefinition | SiUnit |  |

| Source -> Destination |                       |        |  |

<u>Attributes</u>

| Attribute      | Notes                                                      | Default |

|----------------|------------------------------------------------------------|---------|

| factorSiToUnit | This is the factor for the conversion from and to siUnits. |         |

| Float          |                                                            |         |

| offsetSiToUnit | This is the offset for the conversion from and to siUnits. |         |

| Float          |                                                            |         |

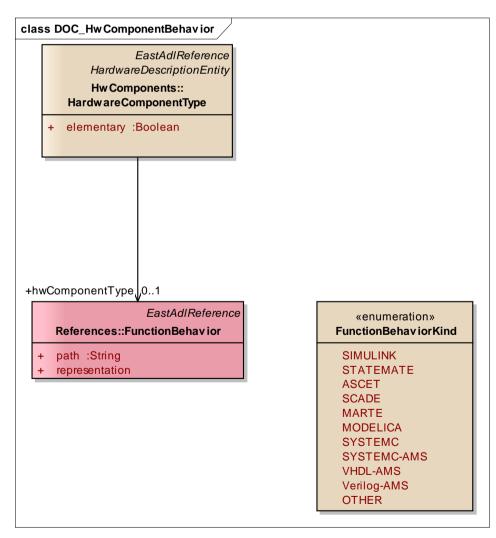

### 9.2.1.2 Package HwComponentBehavior

### Package Notes:

This package describes the behavior of a hardware component. The proposed adaptation of the HardwareComponentType is now the representation of the physical entity of the embedded hardware electrical/electronic component including a hardware behavior. This behavior can be defined by language used during hardware architecture development as SystemC, Modelica, VHDL-AMS or Verilog-AMS.

Figure 3: <u>DOC\_HwComponentBehavior</u> - (Class diagram)

This diagram shows the relation of HardwareComponentType with a FunctionBehavior to map the behavior of the hardware compo a function.

### 9.2.1.2.1 <u>Enumeration</u> FunctionBehaviorKind

Element Base Classes:

Element Notes:

FunctionBehaviorKind is an enumeration which lists the various representations used to describe a FunctionBehavior. It is used as a property of a FunctionBehavior. Hardware modeling language are added to represent the change on behavior attached HardwareComponentType. Several representations are listed; however, one can always extend this list by using the literal OTHER.

Semantics:

It should be noted that though one can use several languages to provide a representation of a FunctionBehavior, the semantics shall remain compliant with the overall EAST-ADL execution semantics (at least at the port a pin interface).

Extension:

Attributes

Enumeration, no extension.

| Attribute   | Notes | Default |

|-------------|-------|---------|

| SIMULINK    |       |         |

| STATEMATE   |       |         |

| ASCET       |       |         |

| SCADE       |       |         |

| MARTE       |       |         |

| MODELICA    |       |         |

| SYSTEMC     |       |         |

| SYSTEMC-AMS |       |         |

| VHDL-AMS    |       |         |

|             |       |         |

© 2012 The SAFE Consortium

| Attribute   | Notes | Default |

|-------------|-------|---------|

| Verilog-AMS |       |         |

| OTHER       |       |         |

|             |       |         |

| 9.2.1.3 | Pac | kage HwC | omponents |

|---------|-----|----------|-----------|

Package Notes:

This package represents the description of the HardwareComponentType and its specializations for precise use, and a compositional approach for hardware component.

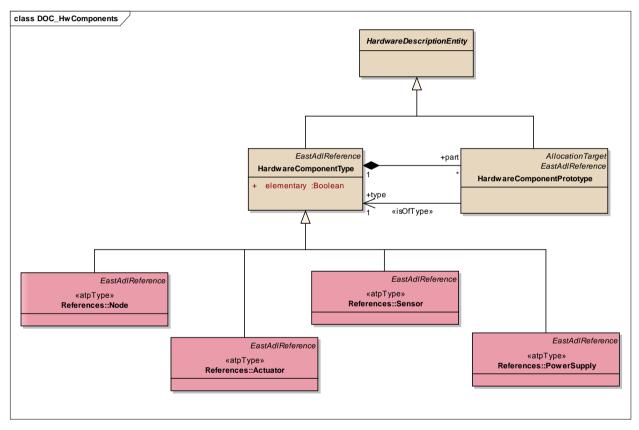

Figure 4: <u>DOC\_HwComponents</u> - (Class diagram)

### Diagram Notes:

This class diagram represents the definition of hardware component and its composition thanks to HardwareComponentType and HardwareComponentPrototype. In addition it includes the list of the class specialized for the use at design level of the hardware component.

#### 9.2.1.3.1 <u>Class</u> HardwareDescriptionEntity

Element Base Classes:

Element Notes:

This abstract class describes any hardware entity for further use.

Semantic:

none

| <i>a</i>   |   |

|------------|---|

| Connection | S |

| Connector                               | Source                     | Target                    |